The ePRTC360+ will be demonstrated at Mobile World Congress (MWC) Barcelona 2026

Bangalore – Feb 18, 2026 – VIAVI Solutions has launched the patent-pending Cesium-less ePRTC360+ holdover solution to safeguard at-risk critical power grids, transportation, aviation and public safety systems, 5G mobile networks and AI data center infrastructure against the increased threat of GNSS timing disruptions. It is the only alternative to Cesium clocks to meet ITU-T G.8272.1 standards.

The international ITU-T G.8272.1 standard stipulates that Enhanced Primary Reference Time Clock (ePRTC) holdover must have short-term drift of less than 30 ns when entering into holdover and a long-term drift of less than 100 ns over 14 days, all traceable to UTC. Previously achieved only by Cesium atomic clocks, VIAVI’s ePRTC360+ now also meets this standard.

“The Cesium-less ePRTC360+ exceeds leading-edge Cesium-level holdover performance and does this for significantly lower price. This enables deployment across the sync network, particularly at edge sites which were previously cost-prohibitive with Cesium holdover clocks,” said Doug Russell, Senior Vice President and General Manager, Aerospace and Defense, VIAVI.

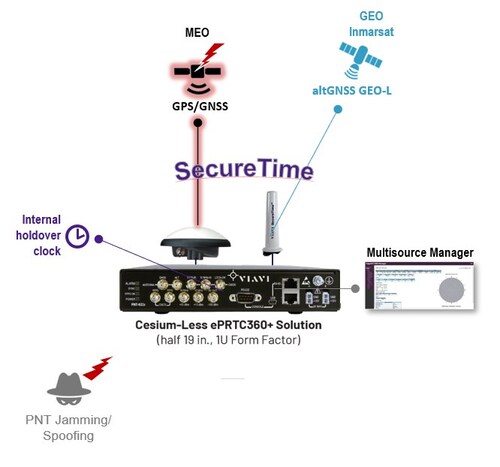

The ePRTC360+ has been successfully tested across a range of live-sky defense and commercial jamming/spoofing environments, and has been integrated into VIAVI’s SecurePNT 6200 product series. The technology can maintain 100 ns accuracy during GNSS-denied threats through the resilient altGNSS GEO-L service with no time limit. It also combines an augmented VIAVI SecureTime GEO anti-jamming antenna and an enhanced GNSS anti-spoofing antenna that also receive eGNSS GEO service with GPS/GNSS-NMA authentication for spoofing detection and mitigation.

Unlike conventional GNSS omni-directional signals, which can be drowned out by low-power interference, VIAVI’s exclusive and GNSS-independent GEO-L service leverages encrypted and highly directional L-band signals transmitted from geostationary satellites. Coupled with the augmented VIAVI SecureTime GEO antenna, the altGNSS GEO-L service provides enhanced anti-jamming protection and a resilient timing reference for the ePRTC360+’s internal Rubidium holdover oscillator and enables smooth multi-orbit source switchover, even when primary GNSS frequencies are jammed, spoofed or subject to sophisticated meaconing attacks.

The affordability of ePRTC360+ clocks compared to Cesium clocks enable operators to deploy them beyond the core and across the network. They also complement non-RF Cesium clocks at the core. This boosts end-to-end sync network robustness and holdover reliability through meshed network PTP feeds as backup between the clocks, especially in case of local or regional jamming and/or spoofing threats.

In addition, the ePRTC360+ addresses constraints posed by the use of Cesium clocks for holdover timing. These include sensitivity to shock, delicate and multi-stage startup procedures that take days to complete, the need for ECCN 3A001.i licenses for export, long GNSS learning period of up to 40 days, as well as strict shipping and storage protocols. In addition, Cesium tubes need to be replaced approximately every seven years, and the dismantling and disposal of Cesium clocks are classified as a hazard due to their material content.

The ePRTC360+ eliminates these hurdles and has been designed for rapid and easy integration into any vendor’s grandmaster clock system. It enables operators to meet stringent ePRTC requirements while reducing total cost of ownership.

The ePRTC360+ will be demonstrated for the first time at VIAVI’s Stand 5B18 at Mobile World Congress (MWC) Barcelona 2026, which takes place March 2-5 in Barcelona, Spain.